31+ memory controller block diagram

Precharge bit lin e to Vdd2 2. This document specifies the functionality of the SRAM memory controller.

Computer System Block Diagram With A Dma Controller And A Pic Computer Architecture Logic Design Engineering Design

Select row Read.

. The online versions of the documents are provided as a courtesy. SDRAM Controller Memory Options 114. 30 17 DDR2mDDR Memory Controller Reset Block Diagram.

23 16 DDR2 Memory Controller Reset Block Diagram. SDRAM Controller Subsystem Block Diagram 113. CS 150 - Spring 2004 Lec 9.

A block diagram of the memory controller IP integrated in the FPGA is showed in Figure 2. The memory controller MC is designed to take Read Write and Read-Modify-Write transactions from the user interface UI block and issues them to memory efficiently. Drive bit l ine 2.

SDRAM Controller Subsystem Block Diagram 123. 31 19 Connecting to Two 8-BitDDR2 SDRAM Devices. 31 Interrupt Masked Register IMR Field Descriptions.

15 DDR2 Memory Controller FIFO Block Diagram. The clock signals for the memory controller are generated by the System Clock Generator SCG. Download scientific diagram Integrated memory controller block diagram.

Memory Controller Architecture 116. 16 DDR2mDDR Memory Controller FIFO Block Diagram. Because the derivation of a 64bit half-key takes at least two passes through the 31-cycle PRESENT.

SDRAM Controller Memory Options 124. Memory Controller - 8 1-Transistor Memory Cell DRAM Writ e. USB OTG Controller Block Diagram and System Integration 193.

USB 20 ULPI PHY Signal. SDRAM Controller Subsystem Interfaces 115. 32-bit Arm Cortex-M0 with 5V Support CAN-FD PTC and Advanced Analog.

A 48-core IA-32 processor in 45 nm CMOS using on-die message-passing and DVFS for. Verify all content and data in the devices PDF. Memory Controller Block Diagram The memory controller handles a maximum of 12 memory banks shared between a general-purpose chip-select machine three user-programmable.

32 20 Module ID and. Cell and b it lin.

Block Diagram Of Computer Block Diagram Diagram Computer

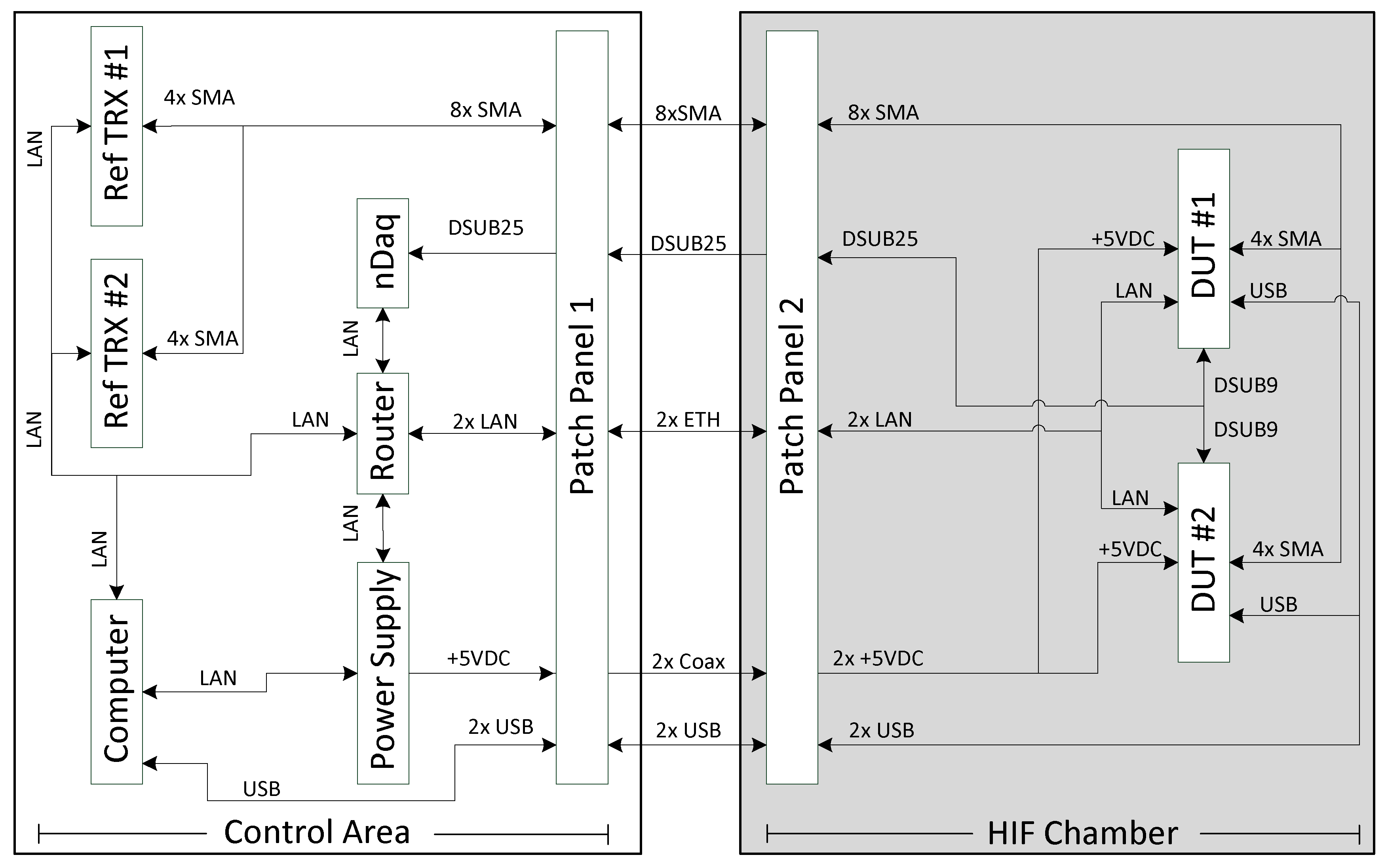

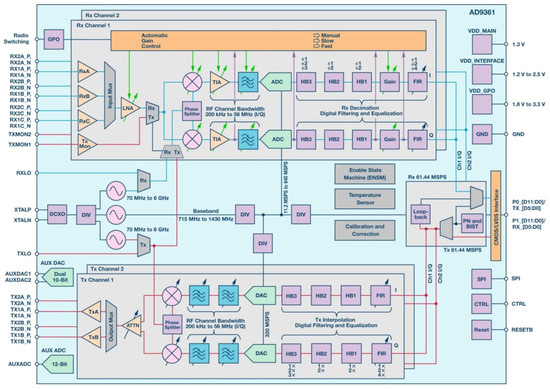

Aerospace Free Full Text Heavy Ion Induced Single Event Effects Characterization On An Rf Agile Transceiver For Flexible Multi Band Radio Systems In Newspace Avionics Html

Ofqmyer9wiee7m

Image 4 Jpg 415 316 Block Diagram Control Unit Coding

Block Diagram Of Computer Block Diagram Diagram Computer System

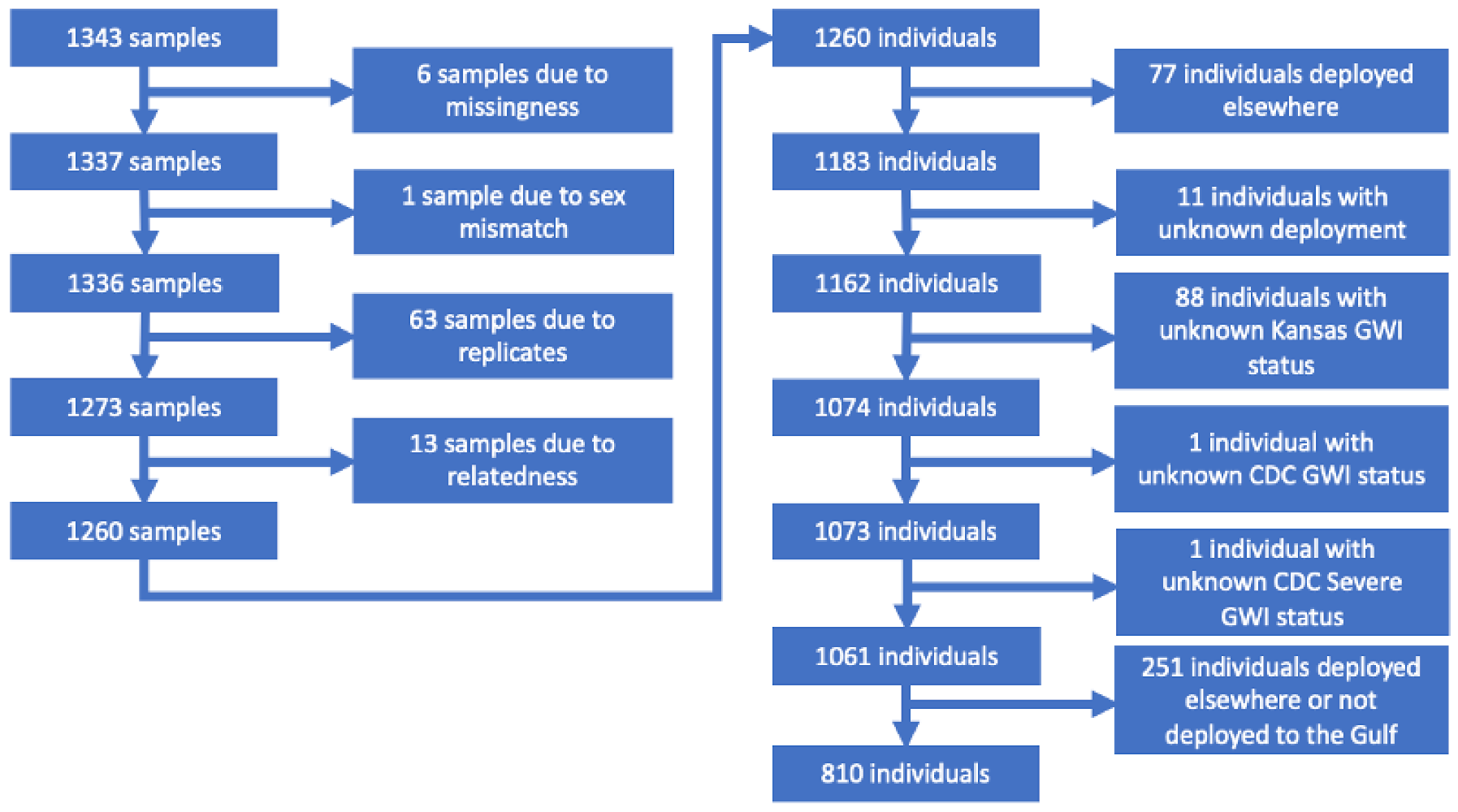

Brain Sciences Free Full Text Gene Ndash Toxicant Interactions In Gulf War Illness Differential Effects Of The Pon1 Genotype Html

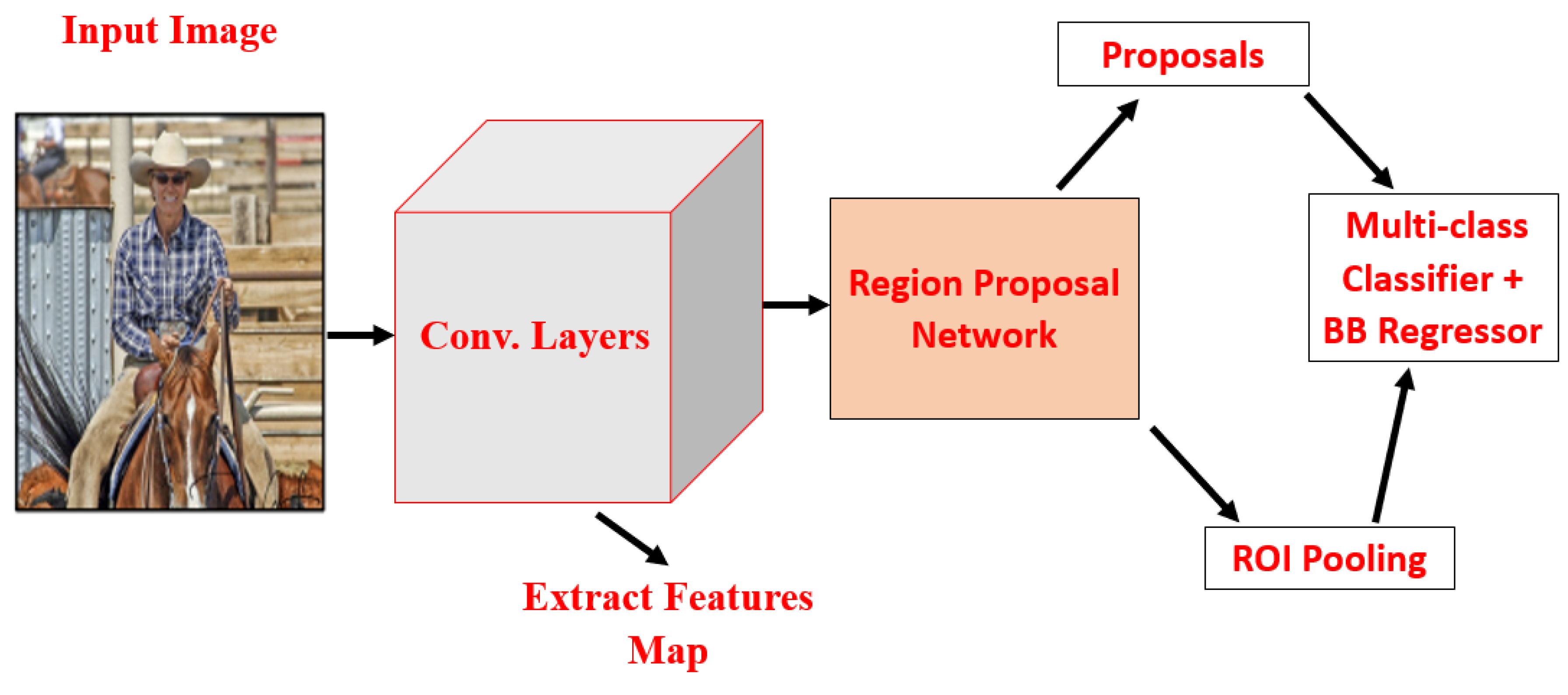

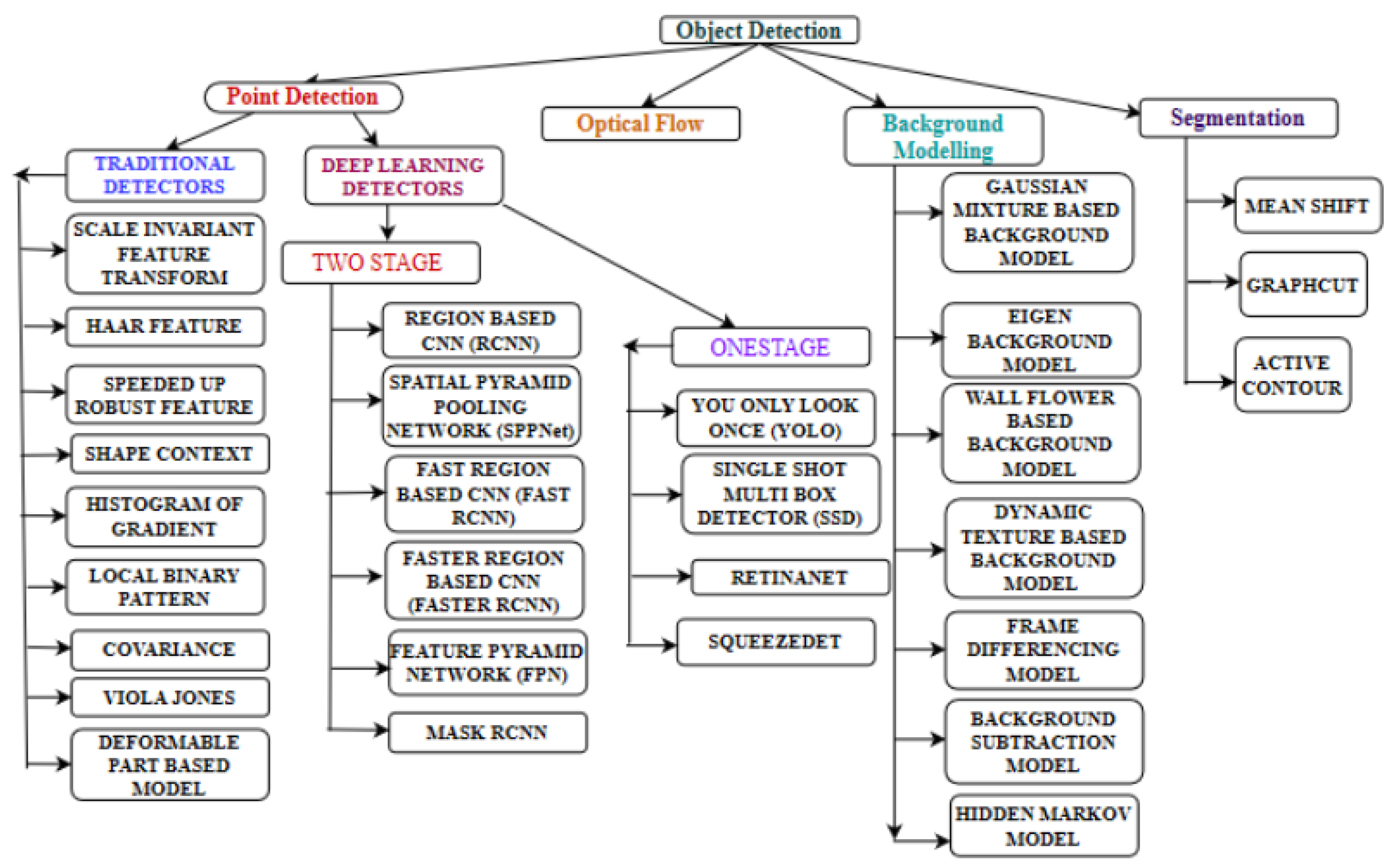

Applied Sciences Free Full Text Investigations Of Object Detection In Images Videos Using Various Deep Learning Techniques And Embedded Platforms A Comprehensive Review Html

2

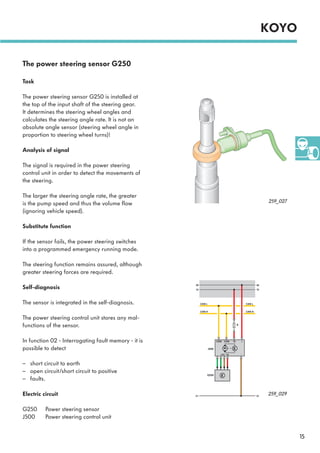

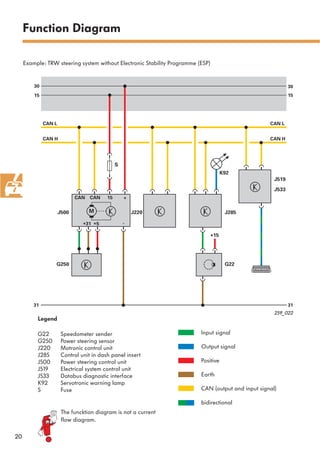

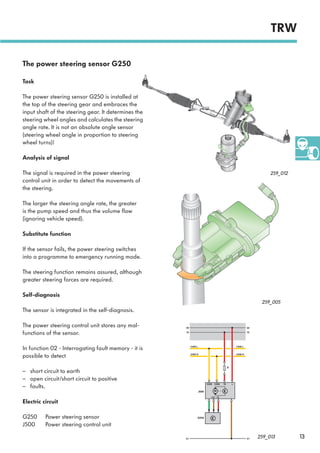

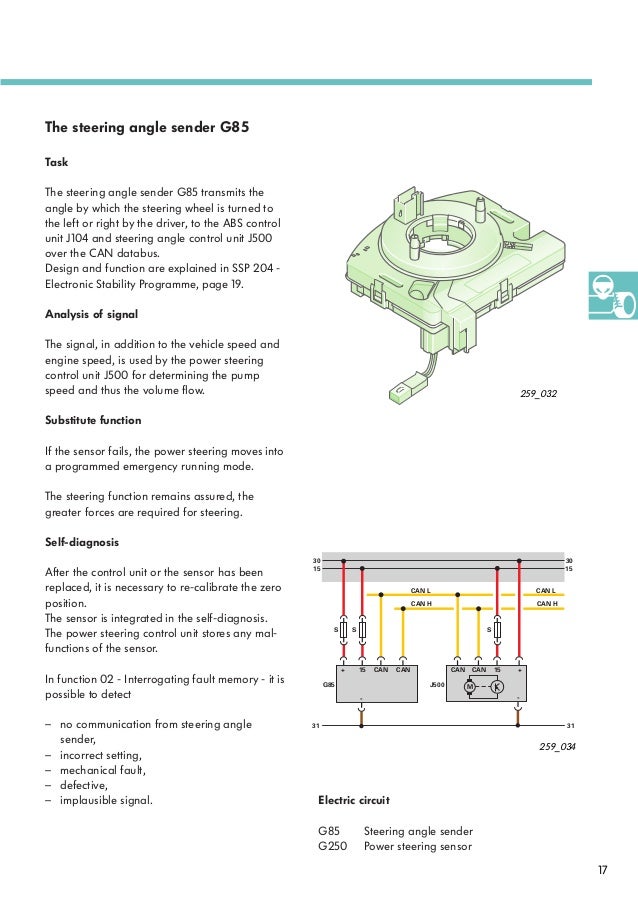

259 Ephs Electrically Powered Hydraulic Steering

259 Ephs Electrically Powered Hydraulic Steering

Launch X431 Pad V Pad5 Full System Professional Diagnostic Tools Support Online Coding And Programming

259 Ephs Electrically Powered Hydraulic Steering

2

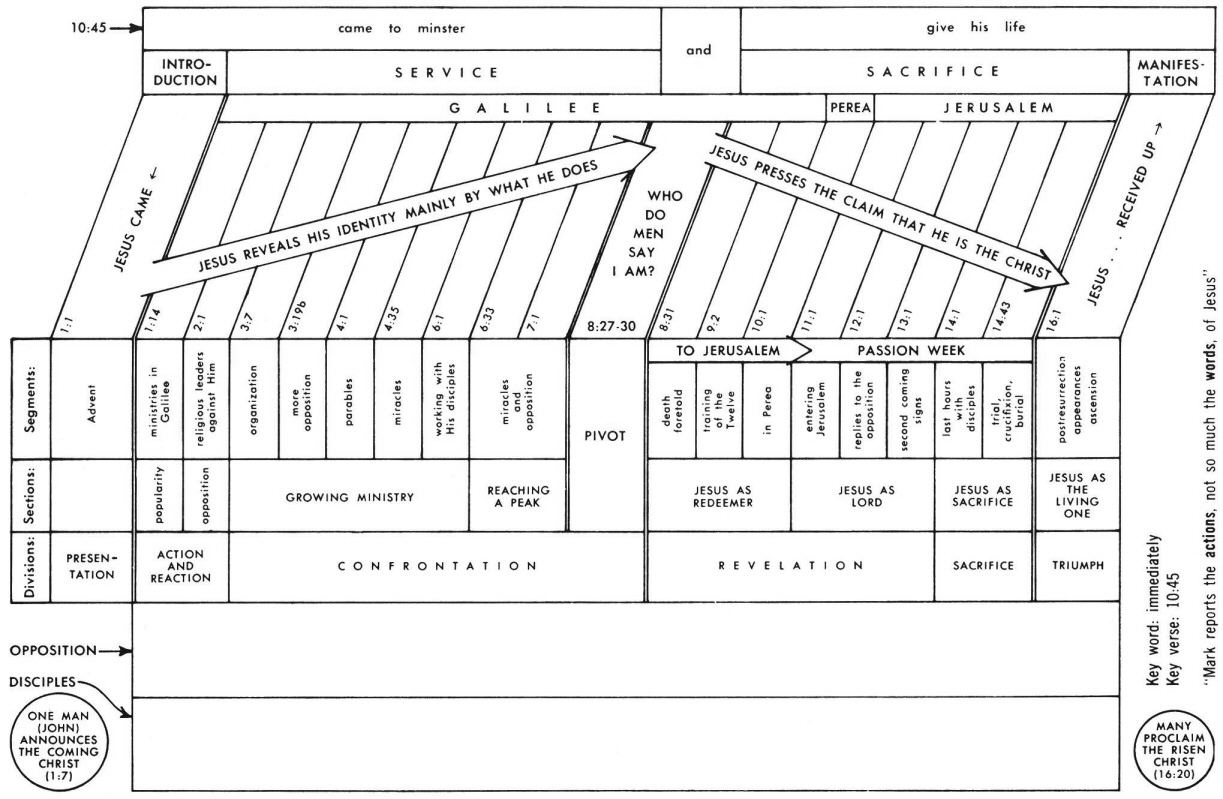

Mark 12 Commentary Precept Austin

259 Ephs Electrically Powered Hydraulic Steering

Applied Sciences Free Full Text Investigations Of Object Detection In Images Videos Using Various Deep Learning Techniques And Embedded Platforms A Comprehensive Review Html

Block Diagram Of Computer Block Diagram Computer Books Estimate Template